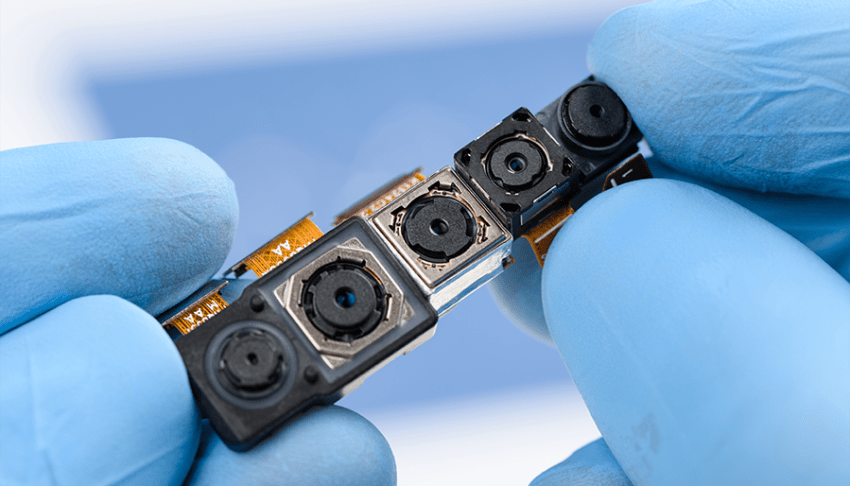

A client chose Nuvation to implement camera input aggregation into their video capture and graphics rendering device. Nuvation’s hardware team provided hardware design, schematics, layout, prototyping, and validation testing. The FPGA design team also provided FPGA design for MIPI camera interfacing and aggregation.

Design Features:

- 8 MIPI camera inputs – 1 lane or 2 lanes, up to 1.5 Gbps/lane

- 1 MIPI output – 4 lane at 2.5 Gbps/lane

- Lattice Crosslink-NX FPGA

- Lattice MIPI PHY IP

- Camera aggregation for input to video processor

- 3D imaging application

Services Provided: